Design And Fpga Implementation For Mac

. Part of the reserve collection (AISC, volume 479) Abstract The Direct Sequence Spread Range, Code Division Multiple Accessibility (DSSS-CDMA) is the one of the moderate access technology in the long term mobile communication techniques because of its possible and immunity against noise.

Synopsys’ FPGA synthesis solution provides Synplify Pro® and Synplify® Premier to accelerate time-to-shipping hardware with deep debug visibility, incremental design, broad language support, and optimal performance and area for FPGA-based products. The practical goal of this paper has been to create a virtual, but practically usable, android home automation system. The android mobile is used to send the commands to the Arduino to control all.

Fpga Implementation Of Turbo Codes

The CDMA offers a exclusive function, i.y., spectrum-spreading procedure which employs a pseudo arbitrary sound (PN) series. These techniques experience from Multiple Access Disturbance. The most important concern in pass on spectrum technique is usually near-far effect. Spreading rules performs a really important part in DSSS-CDMA system. In this papers, DSSS-CDMA system is implemented in VHDL for industry programmable door number (FPGA) so as to eliminate near-far impact for Mobile phone Ad hoc Systems (MANET). Modelsim Xilinx Edition 10.2 (MXE) tool is used for functional simulation simply because well as logic confirmation.

For synthesis, Xilinx Synthesis Technology (XST) of Xilinx ISE device 14.2 is utilized for transmitter and recipient on Virtex 5 FPGA. Aakanksha Devrari. 1. Adesh Kumar. 2. Amit Kumar. 3.

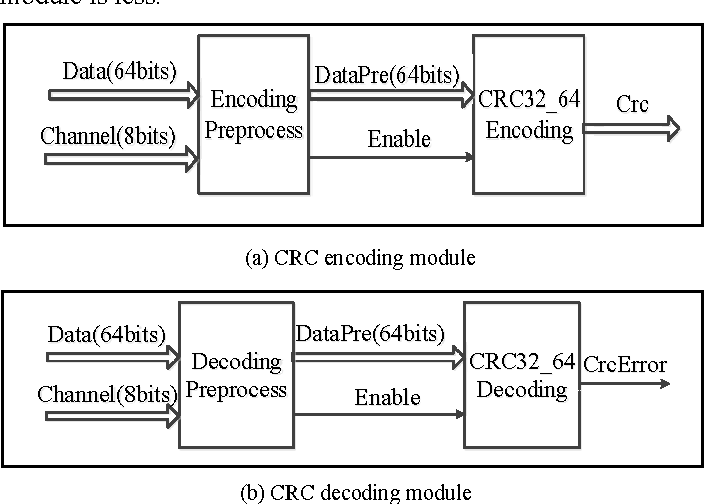

Approach to the implementation of low power digital FIR filter based on field programmable gate arrays (FPGAs).The advantages of the FPGA approach to digital. The MAC layer in EPON system has many functions, such as point-to-point emulation (P2PE), Ethernet MAC functionality, multi-point control protocol (MPCP), network operation, administration and maintenance (OAM) and link security.

Shraddha Singh. 4. 1. Section of Consumer electronics and Communication Engineering Women Company of Technologies (Humor) Dehradun Indian. 2. Ivt bluesoleil v6.4.0 embrace crack only download. Section of Electronics, Instrumentation and Handle Executive (EIC) University of Petroleum and Power Studies (UPES) Dehradun India.

3. Faculty of Technology, Department of VLSI Design Uttarakhand Technical University (UTU) Dehradun Indian. 4. Department of Consumer electronics and Communication Anatomist GLA College Mathura Indian About this document. Cite this document as: Aakanksha Dévrari, Adesh Kumár, Amit Kumar, Shráddha Singh (2017) Design and FPGA Implementation of DSSS fór Near-Far Impact in MANET.

In: Singh L., Choudhury S. (eds) Proceeding of International Meeting on Intelligent Communication, Handle and Gadgets.

Developments in Intelligent Systems and Computing, vol 479. Springer, Singapore. First Online 18 Sept 2016. DOI. Author Name Springer, Singapore. Print out ISBN 978-9-0.

Online ISBN 978-9-7. eBook Deals.

Ethernet unaggressive optical system (EPON), which symbolizes the convergence of low-cost, high-bandwidth and assisting multiple solutions, seems to end up being one of the greatest applicants for the next-generation gain access to network. The work of standardizing EP0N as a option for entry network is nevertheless underway in the IEEE802.3ah Ethernet, in the first kilometer (EFM) job pressure. The final release is usually expected in 2004. Up to right now, there has been no regular application specific integrated signal (ASIC) nick available which meets the functions of media access handle (Mac pc) layer of EPON. The Mac pc layer in EPON program has several functions, like as point-tó-point emulation (G2PE), Ethernet MAC functionality, multi-point control protocol (MPCP), network operation, administration and servicing (OAM) and link protection.

To carry out those functions described above, an embedded real-time operating system (RTOS) and a flexible programmable reasoning device (PLD) with an stuck processor are usually utilized. The software and equipment functions in Mac pc layer are recognized through programming inserted microprocessor and industry programmable door array(FPGA). Finally, some experimental results are given in this papers. The technique stated right here can offer a useful reference point for building EPON Mac pc coating ASIC.